# CENG 336 INT. TO EMBEDDED SYSTEMS DEVELOPMENT

Spring 2006 Recitation 10

## OUTLINE

More about PIC18 Series

Introduction to MCC18

Introduction to PICos18

#### PIC18 Series

#### Features:

- Increased flash (16k words for the PIC18F4520)

- Increased RAM (1536 bytes for the PIC18F4520)

- Extended configuration bits

- Four Crystal modes, up to 40 MHz

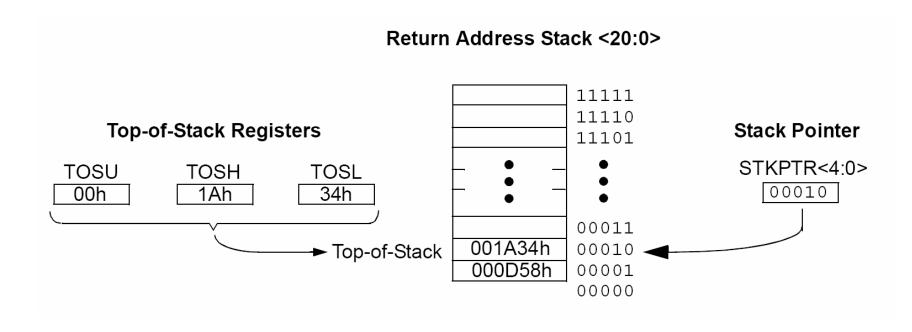

- Much deeper call stack (31 levels deep)

- The call stack may be read and written

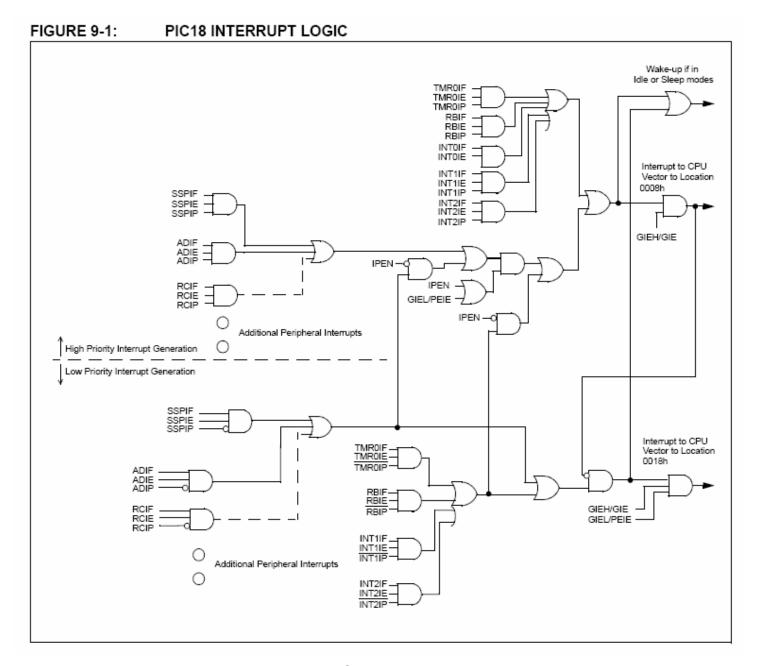

- Two levels of interrupt priority

- Enhanced memory management (can acess the SFRs without switching banks; but not the GPRs)

#### PIC18 Series

#### Features:

- New instructions

- 8x8 hardware multiplier

- Indexed addressing mode (PLUSW)

- Extending the FSR registers to 12 bits, allowing them to linearly address the entire data address space

- C has overtaken assembly

- We will use MPLAB C18 Student Edition.

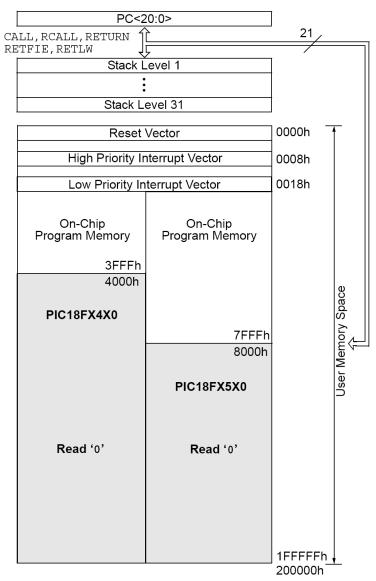

## Program Memory Structure

## Program Memory Structure

#### **EXAMPLE 5-3: INSTRUCTION PIPELINE FLOW**

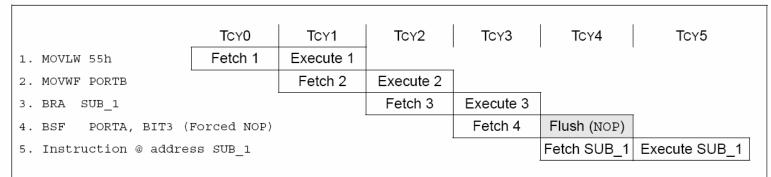

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

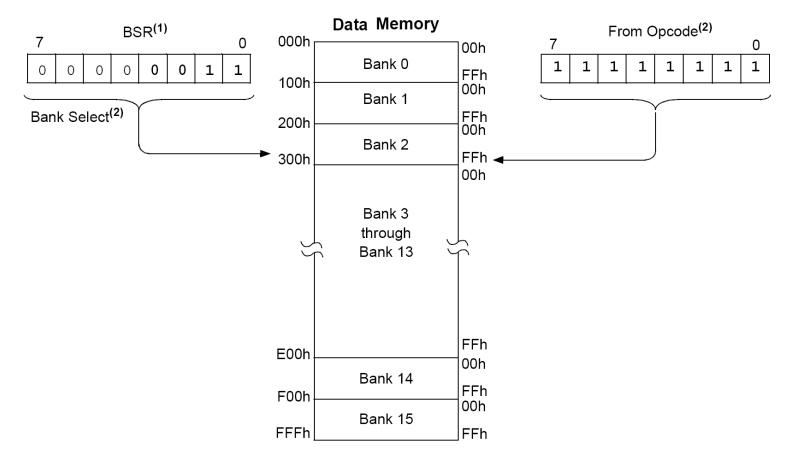

**Note** 1: The Access RAM bit of the instruction can be used to force an override of the selected bank (BSR<3:0>) to the registers of the Access Bank.

2: The MOVFF instruction embeds the entire 12-bit address in the instruction.

**TABLE 5-1:** SPECIAL FUNCTION REGISTER MAP FOR PIC18F2420/2520/4420/4520 DEVICES Address Name Address Name Address Name Address Name FFFh INDF2<sup>(1)</sup> TOSU FDFh **FBFh** CCPR1H F9Fh IPR1 POSTINC2<sup>(1)</sup> FFEh **TOSH FDEh** PIR1 **FBEh** CCPR1L F9Eh POSTDEC2<sup>(1)</sup> FFDh TOSL FDDh **FBDh** CCP1CON F9Dh PIE1 \_\_(2) PREINC2<sup>(1)</sup> **FFCh** STKPTR **FDCh** CCPR2H F9Ch **FBCh** PLUSW2<sup>(1)</sup> FFBh **PCLATU FDBh** CCPR2L F9Bh OSCTUNE **FBBh** \_\_(2) FFAh **PCLATH** FDAh FSR2H **FBAh** CCP2CON F9Ah \_\_(2) \_\_(2) FF9h PCL FD9h FSR2L FB9h F99h \_\_(2) FF8h **TBLPTRU** STATUS **BAUDCON** F98h FD8h FB8h \_\_(2) PWM1CON<sup>(3)</sup> FF7h **TBLPTRH** FD7h TMR0H FB7h F97h ECCP1AS(3) TRISE(3) **TBLPTRL** FF6h FD6h TMR0L FB6h F96h TRISD(3) **TABLAT** CVRCON FF5h FD5h T0CON FB5h F95h \_\_(2) FF4h **PRODH** FD4h FB4h **CMCON** F94h TRISC PRODL TRISB FF3h FD3h OSCCON FB3h TMR3H F93h FF2h INTCON FD2h **HLVDCON** FB2h TMR3L F92h **TRISA** \_\_(2) INTCON2 FF1h FD1h WDTCON FB1h T3CON F91h \_\_(2) INTCON3 **SPBRGH** FF0h FD0h **RCON** FB0h F90h \_\_(2) INDF0<sup>(1)</sup> SPBRG FEFh **FCFh** TMR1H FAFh F8Fh \_\_(2) POSTINCO<sup>(1)</sup> **FEEh FCEh** TMR1L **FAEh RCREG** F8Eh POSTDEC0<sup>(1)</sup> LATE(3) FEDh **FCDh** T1CON FADh **TXREG** F8Dh PREINCO<sup>(1)</sup> LATD(3) **FECh FCCh** TMR2 **FACh** TXSTA F8Ch PLUSW0<sup>(1)</sup> **FEBh FCBh** PR2 FABh **RCSTA** F8Bh LATC \_\_(2) FSR0H LATB FEAh **FCAh** T2CON FAAh F8Ah FE9h FSR0L FC9h SSPBUF FA9h EEADR F89h LATA \_\_(2) FE8h **WREG** FC8h SSPADD FA8h **EEDATA** F88h \_\_(2) INDF1<sup>(1)</sup> FE7h FC7h SSPSTAT EECON2(1) F87h FA7h \_\_(2) POSTINC1<sup>(1)</sup> FE6h FC6h SSPCON1 FA6h EECON1 F86h \_\_(2) \_\_(2) POSTDEC1<sup>(1)</sup> FE5h FC5h SSPCON2 FA5h F85h PREINC1(1) \_\_(2) PORTE<sup>(3)</sup> FE4h FC4h **ADRESH** FA4h F84h \_\_(2) PLUSW1<sup>(1)</sup> FE3h FC3h **ADRESL** FA3h F83h PORTD<sup>(3)</sup> FE2h FSR1H ADCON0 IPR2 **PORTC** FC2h FA2h F82h

FSR1L

FE1h

FE0h

FC1h

FC0h

ADCON1

ADCON2

PIR2

PIE2

FA1h

FA0h

**PORTB**

**PORTA**

F81h

F80h

**BSR** Note 1: This is not a physical register.

<sup>2:</sup> Unimplemented registers are read as '0'.

<sup>3:</sup> This register is not available on 28-pin devices.

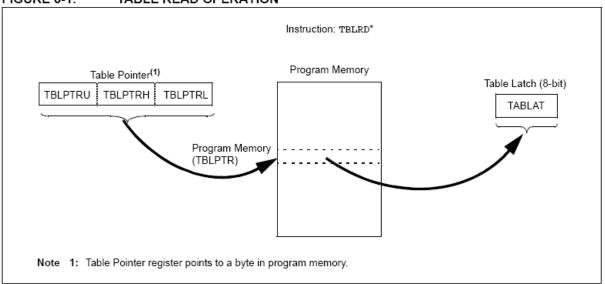

FIGURE 6-1: TABLE READ OPERATION

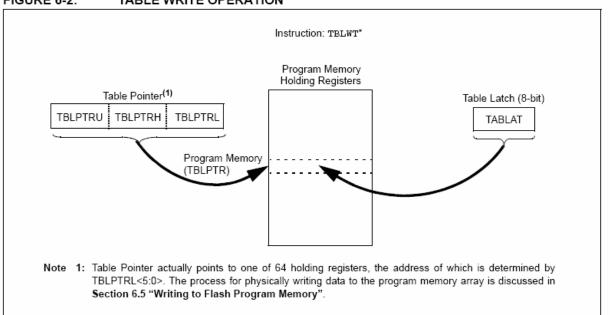

FIGURE 6-2: TABLE WRITE OPERATION

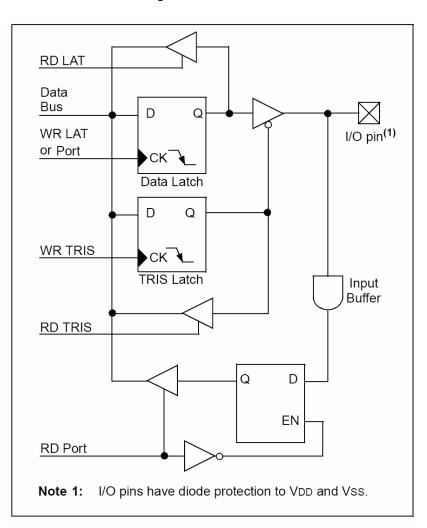

## Some difference in I/O ports

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

In case of bidirectional pins, any read-modify-write instructions intended to change *other* pins of the port should use **LATi** *not* **PORTi**.

### **TIMERS**

#### Timer0:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- Readable and writable registers

- Dedicated 8-bit, software programmable prescaler

- Selectable clock source (internal or external)

- Edge select for external clock

- Interrupt-on-overflow

#### Timer1:

• 16 bit

Timer2, Timer3?

## ENHANCED UNIVERSAL SYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The EUSART can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

#### **ADC MODULE**

- 10-bit 13 channel

- ADCON0, ADCON1, ADCON2 ?

- An acquisition time can be programmed to occur between setting the GO/DONE bit and the actual start of the conversion.

Ex.

ADCON1 (PCFG3:PCFG0) ← 1111; makes all inputs digital i/o

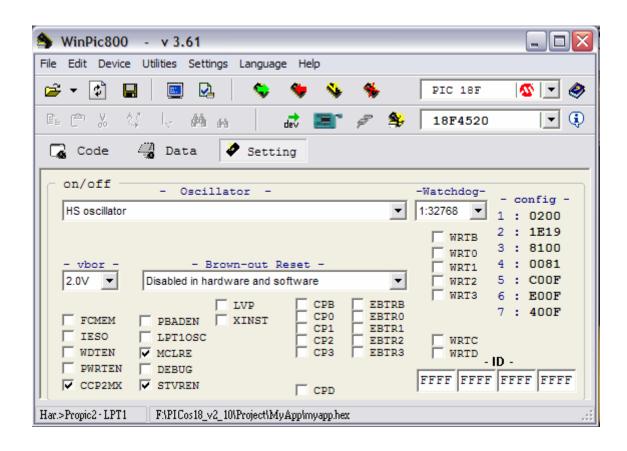

## Configuration bits

#### PICos<sub>18</sub>

A multi-task real-time kernel for PIC18 based on OSEK/VDX™ standart.

- a kernel

- a set of functionalities, services.

- multi-tasking

- multi-task and preemptive (PICos18)

- multi-task and cooperative

- real-time

- priorities

- latency time (determinism)

latency time for PICos: 50 us

### PICos18 Kernel

- ✓ The kernel core (Init + Scheduler + Task Manager) in charge of managing the tasks present in the application and so decide the next task to activate function to the state and the priority oif the tasks.

- ✓ The **alarm and counter manager** (Alarm Manager). Attached to the kernel core it uses the TIMER0 interrupt in order to update periodically the alarms and counters used by the application.

- ✓ The **Hook routines** are partially included in the kernel core and let the developer to jump into additional land personal routines. Doing so it is possible to take the control of the kernel process during a short time to debug the application for instance.

- ✓ The **task manager** (Process Manager) is a set of kernel services which proposes the necessary functions to manage the task state (to change the state of a task, chain two tasks, activate a task...).

- ✓ The **event manager** (Event Manager) is a set of kernel services which proposes the necessary function to manage the events waited or posted by/to a task (to wait for an event, to post an event, to clear an event, to read the set of events received..).

- ✓ The interrupt manager (INT Manager) is a set of kernel services to enable or disable the interrupts (high and low interrupts).